CALL FOR PAPERS

IEEE Open Journal of Nanotechnology (OJ-NANO)

Special Issue on

“In Tribute to Professor Brajesh Kumar Kaushik”

IEEE Open Journal of Nanotechnology (OJ-NANO), a gold fully open access journal launched in 2020 by the IEEE Nanotechnology Council, publishes research advancing the theory, design and development of nanotechnology and its scientific, engineering and industrial applications. The journal has an independent editorial board, an established peer-review process, is targeting a ten-week rapid publishing schedule and is fully compliant with funder mandates, including Plan S. Your work will be exposed to 5 million unique monthly users of the IEEE Xplore® Digital Library. IEEE OJ-NANO received its first Journal Impact of 1.8 and is now indexed in the Science Citation Index Expanded (SCIE)TM by Clarivate Analytics as well as in Scopus®! This development indicates increased visibility and profile for both the journal and its published articles, demonstrating IEEE OJ-NANO is a reliable and high-quality source of information in the field of nanotechnology.

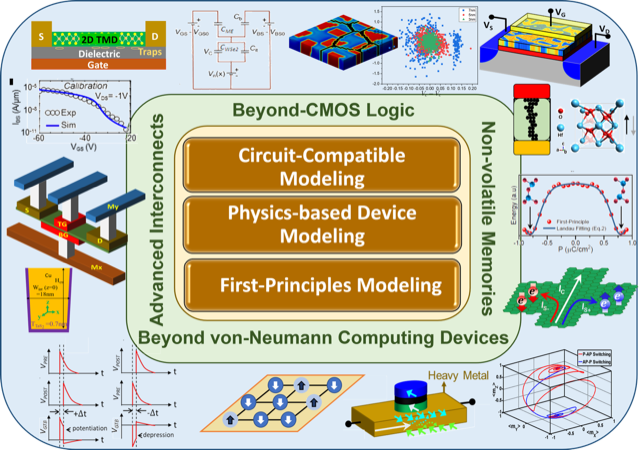

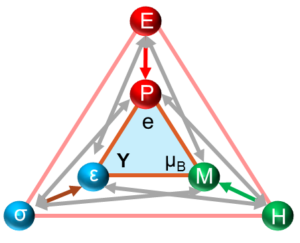

IEEE OJ-NANO will devote a special issue to the memory of Prof. Brajesh Kumar Kaushik who passed away on July 31, 2024. Prof. Kaushik was the coordinator of the IEEE Nanotechnology Council chapters in India, a member of the Administrative Committee of the Council, and a guest editor of special issues on spintronics and neuromorphic computing in the IEEE Transactions on Nanotechnology and IEEE Transactions on Electron Devices. He was a member of the Technical Committee on Spintronics, and a Founding Member of the Technical Committee on Quantum, Neuromorphic and Unconventional Computing. He was an exemplary mentor to many students who are now active researchers in nanotechnology. His enthusiasm and compassion touched many in the nanotechnology community.

NOTE: IEEE OJ-NANO will waive the APC (Article Publishing Charge) for papers invited and accepted for publication in this special issue!

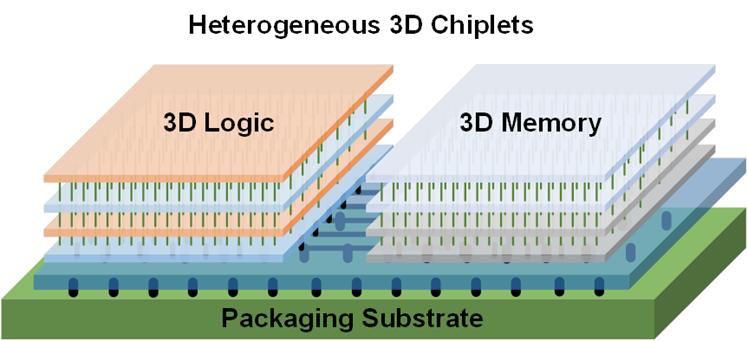

“A call for papers is now open for the IEEE Journal on Exploratory Solid-State Computational Devices and Circuits special topic on “Energy-Efficient In-/Near-Memory Computing with Emerging Devices”.

“A call for papers is now open for the IEEE Journal on Exploratory Solid-State Computational Devices and Circuits special topic on “Energy-Efficient In-/Near-Memory Computing with Emerging Devices”.