NANO BLOG

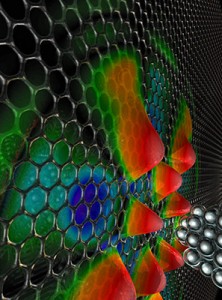

May 9, 2015 – NIST-led Research Group Creates First Whispering Gallery for Graphene Electrons

Yue Zhao et al., an international team of scientists at the U.S. Commerce Department’s National Institute of Standards and Technology (NIST), demonstrated nanoscale whispering gallery electron resonance in graphene by using the probe voltage of a scanning tunneling microscope to create a circular pn junction in nanoscale area like a circular wall of mirrors to the electrons and similar to what happens to acoustic wave in the famous whispering gallery of St. Paul’s Cathedral.

“An electron that hits the step head-on can tunnel straight through it,” said NIST researcher Nikolai Zhitenev. “But if electrons hit it at an angle, their waves can be reflected and travel along the sides of the curved walls of the barrier until they began to interfere with one another, creating a nanoscale electronic whispering gallery mode.”

The potential of graphene-based quantum electronic resonators and lenses is believed to be huge.

Read the original press release and article: Center for Nanoscale Science and Technology/ NIST ; *Y. Zhao, J. Wyrick, F. Natterer, J. Rodriguez-Nieva, C. Lewandowski, K. Watanabe, T. Taniguchi, L. Levitov, N. Zhitenev, and J. Stroscio. Creating and probing electron whispering-gallery modes in graphene. Science. 8 May 2015: Vol. 348, no. 6235, pp. 672-675. DOI: 10.1126/science.aaa7469.

credit: Jon Wyrick, CNST/NIST

(Recommended by Ed Perkins, posted by Yonhua Tzeng)

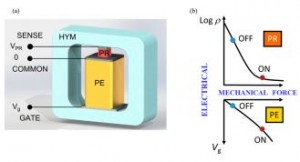

May 8, 2015 – Pathway to the Piezoelectronic Transduction Logic Device

P. M. Solomon et al. proposed a piezoelectronic transistor (PET) not subject to the voltage limits of field-effect transistors. The PET transduces voltage to stress, activating a facile insulator−metal transition, thereby achieving multi-gigahertz switching speeds, as predicted by modeling, at low power. The team demonstrated a stress-based transduction principle. Read the original article: Nano Lett. 2015, 15, 2391−2395.

(Posted by Yonhua Tzeng. Adapted with permission from Nano Lett. 2015, 15, 2391−2395, DOI: 10.1021/nl5046796 Copyright © 2015 American Chemical Society.)

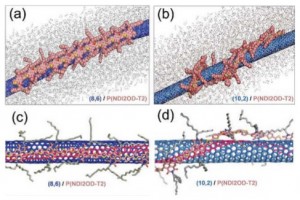

May 8, 2015 – Flexible CMOS-like Logic Circuits Made of N-type Polymer Sorted Single-Wall Carbon Nanotube

Huiliang Wang et al. demonstrated flexible CMOS-like logic circuits made of ambipolar single-wall carbon nanotube transistors fabricated without needing for doping processes using high-mobility electron-accepting (n-type) polymer sorted semiconducting SWCNT. Read the original article: Huiliang Wang et al., Adv. Funct. Mater. 2015, 25, 1837–1844. DOI: 10.1002/adfm.201404126 (Posted by Yonhua Tzeng)

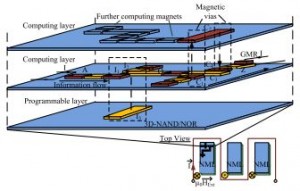

May 7, 2015 – Majority logic gate for 3D nano-scale magnetic computing

Irina Eichwald et al. demonstrated the potential of 3D high integration density digital computing based on physically field interacting nanometer-scaled magnets with a bistable magnetization state, representing the Boolean logic states ‘0’ and ‘1’, arranged in a 3D manner. Read the original article: Irina Eichwald et al 2014 Nanotechnology 25 335202 doi:10.1088/0957-4484/25/33/335202

Schematic of a 3D NML logic system. Logic computing is performed by 3D NAND/NOR gates. Information between functional layers is transmitted by magnetic vias, enabling magnetic signal crossing and computing on a multi-level regime. Electrical in and output sensors enable us to transform magnetic information into the electrical domain and vice versa.

(Posted by Yonhua Tzeng)

May 4, 2015 – Wafer-Level Hysteresis-Free Resonant Carbon Nanotube Transistors

Wafer-level integration of resonant-body carbon nanotube (CNT) field-effect transistors (FETs) of >1M CNTFETs/cm2 with the resonance frequency tunable in situ by both a lateral gate and the back gate has been demonstrated by Ji Cao et al. offering promise in radio frequency signal processing and ultrasensitive sensing.

Adapted with permission from ACS Nano, 2015, 9 (3), pp 2836–2842 DOI: 10.1021/nn506817y. Copyright © 2015 American Chemical Society. (Posted by Yonhua Tzeng)