CALL FOR PAPERS:

IEEE Open Journal of Nanotechnology (OJ-NANO) Special Section on

IEEE-NSENS 2024: Nano Materials and Devices for Sensors, AI, and Robotics

IEEE Open Journal of Nanotechnology (OJ-NANO), a gold fully open access journal launched in 2020 by IEEE Nanotechnology Council, publishes research advancing the theory, design and development of nanotechnology and its scientific, engineering and industrial applications. The journal has an independent editorial board, established peer-review process, is targeting a ten-week rapid publishing schedule and is fully compliant with funder mandates, including Plan S. Your work will be exposed to 5 million unique monthly users of the IEEE Xplore® Digital Library. IEEE OJ-NANO received its first Journal Impact of 1.7 and is now indexed in the Science Citation Index Expanded (SCIE)TM by Clarivate Analytics as well as in Scopus®! This development indicates increased visibility and profile for both the journal and its published articles, demonstrating IEEE OJ-NANO is a reliable and high-quality source of information in the field of nanotechnology.

IEEE OJ-NANO will devote a special section on “IEEE-NSENS 2024: Nano Materials and Devices for Sensors, AI, and Robotics” to a collection of papers highlighting research and technology development in the field of nanotechnology, particular of materials and devices for the applications in sensors, AI and robotics. IEEE Nanotechnology Council sponsors the 3rd IEEE International Conference on Micro/Nano Sensors for AI, Healthcare, and Robotics (IEEE-NSENS 2024) held on 2 – 3 March 2024 to foster interaction between engineers, scientists and industry in these emerging areas.

IEEE OJ-NANO will devote a special section on “IEEE-NSENS 2024: Nano Materials and Devices for Sensors, AI, and Robotics” to a collection of papers highlighting research and technology development in the field of nanotechnology, particular of materials and devices for the applications in sensors, AI and robotics. IEEE Nanotechnology Council sponsors the 3rd IEEE International Conference on Micro/Nano Sensors for AI, Healthcare, and Robotics (IEEE-NSENS 2024) held on 2 – 3 March 2024 to foster interaction between engineers, scientists and industry in these emerging areas.

NOTE: IEEE OJ-NANO will waive 25% of the APC (Article Publishing Charge) for papers accepted for publication in the NANOMED 2023 special issue!

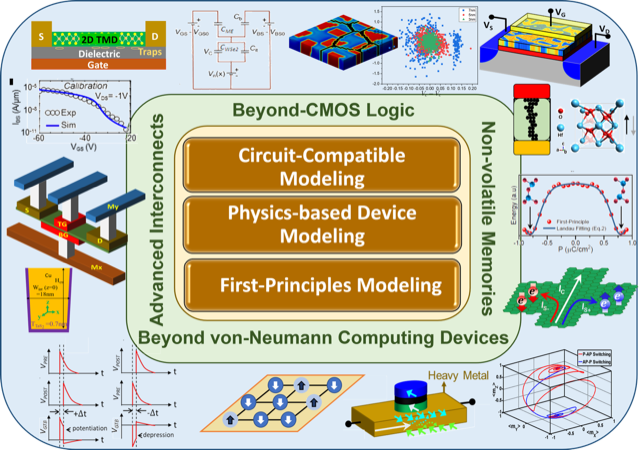

Areas of interest include but are not limited to:

- Micro/Nano Electro – soft electronics

- Micro/Nano Electro – artificial intelligence

- Micro/Nano Electro – bioelectronics

- Micro/Nano Electro – sensors

- Micro/Nano Electro – power electronics

- Micro/Nano Electro – nanobiotechnology

- Micro/Nano Electro – healthcare electronics

- Micro/Nano Electro – medical diagnostics

- Micro/Nano Electro – human-robot interaction

- Micro/Nano Electro – machine learning

- Micro/Nano Electro – deep learning

- Micro/Nano Electro – humanoid robots

- Micro/Nano Electro – flexible sensors

Submissions are solicited from the IEEE-NSENS 2024 conference participants and other researchers in the field for a review paper or a research paper for this themed issue. Manuscripts will be subject to the OJ-NANO normal peer review procedures. If your manuscript is based on the IEEE-NANOMED 2023 paper, the manuscript must build significantly on it, with at least 30% of the submitted results representing new research. Additional text, figures and references are obligatory, and no passages of texts or figures should be identical to your conference paper as this could breach copyright. A nearly exact duplicate of the conference paper will be rejected.

Manuscripts for IEEE OJ-NANO must be prepared using the “IEEE manuscript template” and “Information for Authors” at https://oj-nano.ieeenano.org/submitting-an-article/; and be submitted on-line via the IEEE Manuscript Central found at https://mc.manuscriptcentral.com/oj-nano. On submission to IEEE OJ-NANO, authors should select the “Special Issue: IEEE-NANOMED 2023” as a manuscript type instead of “Regular Paper.” Also, indicate in the cover letter that you wish the paper to be considered for the Special Issue “Nano/Molecular Medicine and Engineering”.

Deadlines:

| Manuscript Submission | April 30, 2024 |

| Anticipated Publication | November 31, 2024 |

Guest Editors:

Yunlong Zi, Ph.D.

Associate Professor, Sustainable Energy and Mechanical Engineering

Hong Kong University of Science and Technology – Guangzhou, China

Email: ylzi@hkust-gz.edu.cn

Kewang Nan, Ph.D.

Professor, Micro Nano Materials and Biomedical Engineering

Zhejiang University, China

Email: knan@zju.edu.cn